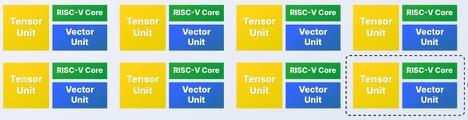

Ventana i Cupertino släpper version två av sin Risc V-serverdesign Veyron. Den kan klämma in dubbelt så många cpu:er som ettan – 32 mot 16 – och ska tillverkas i 4 nm hos TSMC.

Ventana i Cupertino släpper version två av sin Risc V-serverdesign Veyron. Den kan klämma in dubbelt så många cpu:er som ettan – 32 mot 16 – och ska tillverkas i 4 nm hos TSMC.

Veyron V1 släpptes i december för mindre än ett år sedan. V2 presenteras på konferensen Risc V Summit den 7–8 november.

Pusslar du ihop sex V2-chiplets kan du komma upp i sammanlagt 192 cpu:er som kan klockas till 3,6 GHz. Cacheminnet är på 128 kbyte L1 och 1 MB L2. 32 cpu:er i ett kluster har ett gemensamt L3-cache på 128 MB.

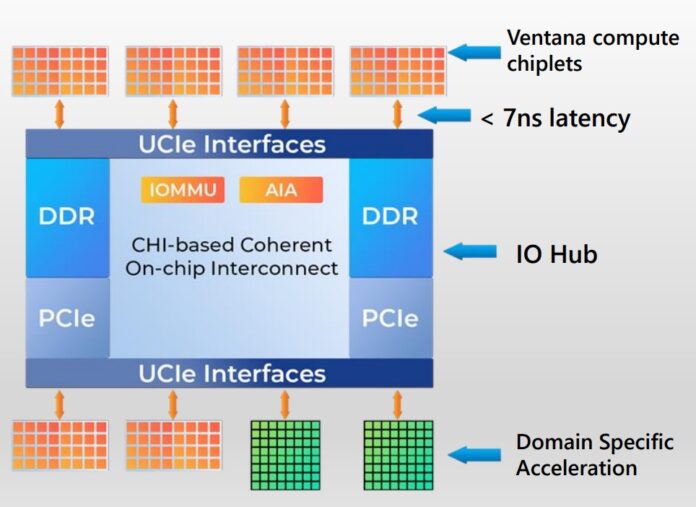

Utrymme finns i designen för att addera skräddarsydda acceleratorblock. De kallas DSA:er, Domain Specific Accelerators, och kan exempelvis användas för komprimering, kryptering, datapaketprocessning eller databasoperationer.

Veyron V1 och V2 är avsedda för datacenter. V2 stöder virtualisering av typ 1 och 2. Den stöder även IOMMU (Input-Output Memory Management Unit) vilket ger virtualiserade enheter direkt access till minnet. Här finns även gränssnitt för debug, trace och prestandamonitorering.

V2 har växlat till UCIE (Universal Chiplet Interconnect) från V1:s BoW (Bunch of Wires). UCIE har bättre prestanda, och 46 potentiella V2-kunder var eniga om det var den de ville ha i diskussioner med Ventana.

Risc V finns i flera profiler och den som V2 stöder är RVA23 (Risc V Application 2023) vilket bland annat implicerar att den stöder vektorinstruktioner i 512 bitar.

V2 har även ett tillägg som Ventana kallar ”AI Matrix Extensions” som accelerar vad det låter som. V1 hade varken vektor- eller matrisoperationer. De betyder att V2 konkurrerar bättre mot neuronnätsinferenser när de dras i cpu:n snarare än delegeras till en dedikerad neuronkärna.

|

| Processor kring sex V2-chiplettar och två DSA-acceleratorer. |

V1 och V2 kan licenseras som IP, men kanske framför allt ska de tillverkas som chiplets i fyra respektive 5 nm för integerering med chiplets från partners för exempelvis PCI Express, nätverk, minne och förbindning.

Fysiska V2-chiplets beräknas finnas tillverkade under andra halvan av 2024.

The Next Platform har en djupare analys av V2. En av spaningarna är att det tog Intel 15 år att ta sig in på processormarknaden för datacenter och tio år för Arm. För Risc V gissar The Next Platform att det kanske bara kommer att ta fem år.

Cpu-arkitekturen Risc V är en licensfri standard som lanserades 2014. Dagens dominerande cpu-arkitekturer är den privata X86 och den licenserade Arm.

Bilden ovan är bara en illustration